Tabel kebenaran dan Diagram Waktu Teknik Digital

Tabel kebenarannya (truth table) dan Diagram waktunya - Teknik Digital

Pendahluan

Gerbang logika hanya mampu mengubah sinyal keluaran sejalan dengan sinyal masukan. Bagaimana bentuk ragam gelombang dari perubahan sinyal tersebut tergantung pada gerbang logikanya. Prinsip dasar dari gerbang logika dan kombinasional adalah perubahan keadaan level keluaran tergantung dari keadaan masukan, untuk setiap saat dari waktu ke waktu. Jika setiap keadaan masukan berubah maka gerbang logika akan berubah pula kaluarannya saat itu juga. Jadi rangkaian gerbang logika hanya berfungsi menyiapkan suatu operasi logika kemudian hasil dinyatakan pada keluaran.

Pada contoh diatas dapat dilihat kedua sinyal yang masuk pada gerbang nor saat itu juga diberikan keluarannya yang terdiri atas satu sinyal.

Dengan membuat gerbang logika kombinasional kita dapat membuat rangkaian yang dapat menyimpan data. Rangkaian inilah yang disebut rangkaian Flip Flop. Fliop Flop merupakan piranti yang dapat menyimpan 1 bit data yaitu 1 atau 0.

Pada contoh diatas dapat dilihat kedua sinyal yang masuk pada gerbang nor saat itu juga diberikan keluarannya yang terdiri atas satu sinyal.

Dengan membuat gerbang logika kombinasional kita dapat membuat rangkaian yang dapat menyimpan data. Rangkaian inilah yang disebut rangkaian Flip Flop. Fliop Flop merupakan piranti yang dapat menyimpan 1 bit data yaitu 1 atau 0.

Lambang dan Notasi

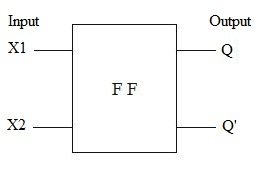

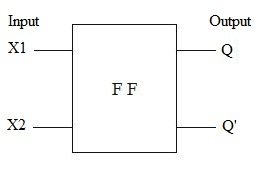

Terdapat berbagai jenis flip flop, masing masing flip flop memmiliki lambang dan notasi yang berbeda. Tetapi semuanya memiliki dasar lambang yang sama yaitu sebuah kotak dangan garis depan yang berupa input dan garis belakang yang berupa output sedangkan kotak merupakan rangkaian flip flop.

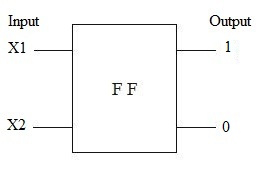

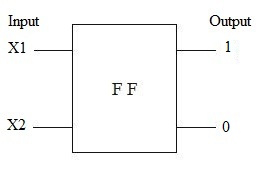

Gambar tersebut menunjukkan dua keluaran yang di wakili huruf Q dan Q’ yang mana nilai Q’ selalu terbalik terhadap Q, dua sinyal masukan yang diwakili huruf X1 dan X2, dan kotak ditengah yang diberi huruf FF merupakan rangkaian flip flop.

Gambar tersebut menunjukkan dua keluaran yang di wakili huruf Q dan Q’ yang mana nilai Q’ selalu terbalik terhadap Q, dua sinyal masukan yang diwakili huruf X1 dan X2, dan kotak ditengah yang diberi huruf FF merupakan rangkaian flip flop.

Seperti pada gambar diatas, keluaran Q bernilai 1 maka Q’ yang dihasilkan adalah 0

Seperti pada gambar diatas, keluaran Q bernilai 1 maka Q’ yang dihasilkan adalah 0

Antara Multivibrator dan Flip Flop

Piranti flip flop juga sering disebut Multivibrator Bistabil. Istilah ini sering digunkan untuk jenis tertentu dari flip flop. Istilah ini biasanya digunakan untuk membahas prinsip kerja rangkaian dasar. Sedangkan istilah flip flop sering digunakan untuk membicarakan keseluruhan rangkaian. Sesungguhnya multivibrator dan flip flop memiliki prinsip kerja yang sama.

A. Flip Flop RS (Reset Set Flip Flop)

Dengan menggunakan gabungan gerbang – gerbang logika menjadi suatu gerbang logika kombinasional dan kemudian diumpan balikkan. Lalu dapat dibangun suatu rangkaian logika yang dapat menyimpan data. Rangkaian logika ini disebut dengan piranti atau rangkaian flip flop. Flip Flop ini adalah elemen memori terkecil yang dapat menyimpan data sebesar 1 bit, yaitu 0 atau 1. Flip Flop juga merupakan piranti yang memiliki dua keadaa stabil. Piranti ini akan tetap bertahan padansalah satu keadaan itu sampai ada pemicu yang membuatnya berganti keadaan.

Dengan menggunakan gabungan gerbang – gerbang logika menjadi suatu gerbang logika kombinasional dan kemudian diumpan balikkan. Lalu dapat dibangun suatu rangkaian logika yang dapat menyimpan data. Rangkaian logika ini disebut dengan piranti atau rangkaian flip flop. Flip Flop ini adalah elemen memori terkecil yang dapat menyimpan data sebesar 1 bit, yaitu 0 atau 1. Flip Flop juga merupakan piranti yang memiliki dua keadaa stabil. Piranti ini akan tetap bertahan padansalah satu keadaan itu sampai ada pemicu yang membuatnya berganti keadaan.

Penahan NOR (NOR Latch)

Flip Flop dengan penahan NOR dibangun dengan mengggunakan rangkaian terpadu (IC). Flip Flop yang dibangun dengan menggunakan gerbang logika NOR dinamakan penahann NOR.

Rangkaian Flip Flop SR Penahan NOR

Tabel Kebenaran

Tabel Kebenaran

Diagram Masukan

Diagram Masukan

Penahan NOR dapat dinyatakan kembali dengan teorema De morgan, sehingga kita dapatkan rangkaian penahan yang lain tetapi dengan fungsi yang sama

Flip Flop SR dengan gerbang NOT dan AND

Penahan NOR dapat dinyatakan kembali dengan teorema De morgan, sehingga kita dapatkan rangkaian penahan yang lain tetapi dengan fungsi yang sama

Flip Flop SR dengan gerbang NOT dan AND

Masukkan R dalam keadaan 0 dan S dalam keadaan 1 memberikan keadaan SET. Sedangkan apabila R dalam keadaan 1 dan S dalam keadaan 0 akan memberikan keadaan RESET. Namun saat SET dan RESET dalam keadaan 1, akan terjadi keadaan pacu. Oleh karena itu kita harus menghinari keadaan R dan S dalam keadaan 1. Sedangkan Saat S dan R dalam keadaan 0, tidak terjadi perubahan.

Prinsip Kerja Penahan NOR.

1. Pengujian Rankaian.

Diagram Masukan

Masukkan R dalam keadaan 0 dan S dalam keadaan 1 memberikan keadaan SET. Sedangkan apabila R dalam keadaan 1 dan S dalam keadaan 0 akan memberikan keadaan RESET. Namun saat SET dan RESET dalam keadaan 1, akan terjadi keadaan pacu. Oleh karena itu kita harus menghinari keadaan R dan S dalam keadaan 1. Sedangkan Saat S dan R dalam keadaan 0, tidak terjadi perubahan.

Prinsip Kerja Penahan NOR.

1. Pengujian Rankaian.

Diagram Masukan

Apabila S rendah (0), maka keluaran Q akan rendah, walaupun keadaan R dirubah mejadi tinggi maupun rendah, maka Q tetap rendah.

2. Keadaan SET.

Diagram Masukan

Apabila S dalam keadaan 1 (tinggi) keluaran Q akan 1 (tinggi). dan S hanya sekali memberikan pulsa, dari keadaan 0 menjadi 1. Sesudah itu jika keadaan S berubah-rubah , keluaran Q akan tetap 1.

3. Keadaan RESET.

Diagram Masukan

Pada keadaan ini, keluaran Q tetap 1 (tinggi) apapun yang terjadi pada S. Cara menurunkan atau mengubah keadaan dengan menurunkan pulsa dari 1 menjadi 0 adalah dengan cara mengaktifkan R. Begitu R berubah keadaannya dari 0 menjadi 1 maka seketika itu juga keluaran Q akan menjadi 0 (rendah). Sesudah itu, apapun yang terjadi pada masukan R, flip flop tidak akan menganggapi.

Diagram Masukan

Saat ingin mengubah keadan keluaran Q lagi maka S harus diberi pulsa kembali, maka keluaran Q akan menjadi 1. Untuk mengubahnya menjadi 0 lagi maka R diberi pulsa kembali.

4. Keadaan HOLD .

Fllip Flop dinyatakan dalam keadaan Hold jika data yang dimasukkan pada flip flop ditahan, hingga ada perubahan masukan. Langkah langkah percobaan diatas adalah suatu cara untuk mengetahui prinsip kerja dari flip flop secara bertahap dan terstruktur, dan dari percobaan tersebut telah dibukrikan bahwa flip flop dapat menyimpan data dengan cara menahan data tersebut.

Flip Flop dengan penahan NOR dibangun dengan mengggunakan rangkaian terpadu (IC). Flip Flop yang dibangun dengan menggunakan gerbang logika NOR dinamakan penahann NOR.

Rangkaian Flip Flop SR Penahan NOR

Tabel Kebenaran

Diagram Masukan

Penahan NOR dapat dinyatakan kembali dengan teorema De morgan, sehingga kita dapatkan rangkaian penahan yang lain tetapi dengan fungsi yang sama

Flip Flop SR dengan gerbang NOT dan AND

Masukkan R dalam keadaan 0 dan S dalam keadaan 1 memberikan keadaan SET. Sedangkan apabila R dalam keadaan 1 dan S dalam keadaan 0 akan memberikan keadaan RESET. Namun saat SET dan RESET dalam keadaan 1, akan terjadi keadaan pacu. Oleh karena itu kita harus menghinari keadaan R dan S dalam keadaan 1. Sedangkan Saat S dan R dalam keadaan 0, tidak terjadi perubahan.

Prinsip Kerja Penahan NOR.

1. Pengujian Rankaian.

Diagram Masukan

Apabila S rendah (0), maka keluaran Q akan rendah, walaupun keadaan R dirubah mejadi tinggi maupun rendah, maka Q tetap rendah.

2. Keadaan SET.

Diagram Masukan

Apabila S dalam keadaan 1 (tinggi) keluaran Q akan 1 (tinggi). dan S hanya sekali memberikan pulsa, dari keadaan 0 menjadi 1. Sesudah itu jika keadaan S berubah-rubah , keluaran Q akan tetap 1.

3. Keadaan RESET.

Diagram Masukan

Pada keadaan ini, keluaran Q tetap 1 (tinggi) apapun yang terjadi pada S. Cara menurunkan atau mengubah keadaan dengan menurunkan pulsa dari 1 menjadi 0 adalah dengan cara mengaktifkan R. Begitu R berubah keadaannya dari 0 menjadi 1 maka seketika itu juga keluaran Q akan menjadi 0 (rendah). Sesudah itu, apapun yang terjadi pada masukan R, flip flop tidak akan menganggapi.

Diagram Masukan

Saat ingin mengubah keadan keluaran Q lagi maka S harus diberi pulsa kembali, maka keluaran Q akan menjadi 1. Untuk mengubahnya menjadi 0 lagi maka R diberi pulsa kembali.

4. Keadaan HOLD .

Fllip Flop dinyatakan dalam keadaan Hold jika data yang dimasukkan pada flip flop ditahan, hingga ada perubahan masukan. Langkah langkah percobaan diatas adalah suatu cara untuk mengetahui prinsip kerja dari flip flop secara bertahap dan terstruktur, dan dari percobaan tersebut telah dibukrikan bahwa flip flop dapat menyimpan data dengan cara menahan data tersebut.

Penahan NAND (NAND Latch)

Sebuah Flip Flop RS yang terbuat dari gerbang logika NAND (NOT-AND) sering disebut sebagai penahan NAND. Penahan NAND prinsip kerjanya sama dengan NOR. Perbedaannya terletak pada keadaan level atau tingkat logikanya. Masukan – masuka SET dan RESET dari penahan NOR bekerja dari keadaan O menjadi 1, sewaktu mengubah keadaan, sedangkan penahan NAND sebaliknya. Masukan – masukan SET dan RESET dari penahan NAND bekerja dari keadaan 1 menjadi 0 sewaktu mengubah keadaan.

Penahan NAND

Tabel Kebenaran

Tabel Kebenaran

Diagram Masukan

Diagram Masukan

Penahan NAND dapat dinyatakan kembali dengan teorema De Morgan, sehingga kita dapatkan rangkaian penahan yang lain tetapi fungsi logikanya sama.

Flip Flop SR gerbang OR dan NOT

Penahan NAND dapat dinyatakan kembali dengan teorema De Morgan, sehingga kita dapatkan rangkaian penahan yang lain tetapi fungsi logikanya sama.

Flip Flop SR gerbang OR dan NOT

Penahan NAND juga dapat dibangun dengan gerbang logika NAND silang (Cross NAND) dan disebut dengan Flip Flop SR NAND Silang (Cross NAND SR Flip Flop)

Flip Flop SR gerbang NAND Silang

Penahan NAND juga dapat dibangun dengan gerbang logika NAND silang (Cross NAND) dan disebut dengan Flip Flop SR NAND Silang (Cross NAND SR Flip Flop)

Flip Flop SR gerbang NAND Silang

Tabel Kebenaran

Tabel Kebenaran

Prinsip Kerja dari penahan NAND.

1. Keadaan Pengujian.

Diagram Masukan

Prinsip Kerja dari penahan NAND.

1. Keadaan Pengujian.

Diagram Masukan

Apabila S = 1 (tinggi) maka keluaran Q akan rendah. Walaupun R diubah-ubah keadaannya, keadaannya tetap 0.

2. Keadaan SET.

Diagram Masukan

Apabila S = 1 (tinggi) maka keluaran Q akan rendah. Walaupun R diubah-ubah keadaannya, keadaannya tetap 0.

2. Keadaan SET.

Diagram Masukan

Apabila S berubah dari 1 menjadi 0, maka keluaran Q akan langsung 1. Dan S hanya sekali saja membuat pulsa dari keadaan 0 menjadi 1. Sesudah itu jika keadaan S akan berubah ubah, keluaran tetap 1. Yang artinya penahan NAND akan tetap menahan data pertama yang masuk, selama dalam keadaan ini penahan NAND berada dalam keadaan HOLD

3. Keadaan RESET.

Diagram Masukan

Apabila S berubah dari 1 menjadi 0, maka keluaran Q akan langsung 1. Dan S hanya sekali saja membuat pulsa dari keadaan 0 menjadi 1. Sesudah itu jika keadaan S akan berubah ubah, keluaran tetap 1. Yang artinya penahan NAND akan tetap menahan data pertama yang masuk, selama dalam keadaan ini penahan NAND berada dalam keadaan HOLD

3. Keadaan RESET.

Diagram Masukan

Pada keadaan ini, keluaran Q tetap 1 (tinggi) apapun yang terjadi pada S. Cara menurunkan pulsa dari 1 menjadi 0 adalah mengaktifkan R. Begitu R berubah keadaannya dari 1 menjadi 0 maka seketika itu juga keluaran Q akan menjadi 0. Dan R hanya sekali saja berperan dalam mengubah keadaan keluaran Q. Setelah itu apapun yang terjadi pada R tidak akan ditangga pi oleh keluaran Q.

REFERENSI :

Pada keadaan ini, keluaran Q tetap 1 (tinggi) apapun yang terjadi pada S. Cara menurunkan pulsa dari 1 menjadi 0 adalah mengaktifkan R. Begitu R berubah keadaannya dari 1 menjadi 0 maka seketika itu juga keluaran Q akan menjadi 0. Dan R hanya sekali saja berperan dalam mengubah keadaan keluaran Q. Setelah itu apapun yang terjadi pada R tidak akan ditangga pi oleh keluaran Q.

REFERENSI :

Sebuah Flip Flop RS yang terbuat dari gerbang logika NAND (NOT-AND) sering disebut sebagai penahan NAND. Penahan NAND prinsip kerjanya sama dengan NOR. Perbedaannya terletak pada keadaan level atau tingkat logikanya. Masukan – masuka SET dan RESET dari penahan NOR bekerja dari keadaan O menjadi 1, sewaktu mengubah keadaan, sedangkan penahan NAND sebaliknya. Masukan – masukan SET dan RESET dari penahan NAND bekerja dari keadaan 1 menjadi 0 sewaktu mengubah keadaan.

Penahan NAND

Tabel Kebenaran

Diagram Masukan

Penahan NAND dapat dinyatakan kembali dengan teorema De Morgan, sehingga kita dapatkan rangkaian penahan yang lain tetapi fungsi logikanya sama.

Flip Flop SR gerbang OR dan NOT

Penahan NAND juga dapat dibangun dengan gerbang logika NAND silang (Cross NAND) dan disebut dengan Flip Flop SR NAND Silang (Cross NAND SR Flip Flop)

Flip Flop SR gerbang NAND Silang

Tabel Kebenaran

Prinsip Kerja dari penahan NAND.

1. Keadaan Pengujian.

Diagram Masukan

Apabila S = 1 (tinggi) maka keluaran Q akan rendah. Walaupun R diubah-ubah keadaannya, keadaannya tetap 0.

2. Keadaan SET.

Diagram Masukan

Apabila S berubah dari 1 menjadi 0, maka keluaran Q akan langsung 1. Dan S hanya sekali saja membuat pulsa dari keadaan 0 menjadi 1. Sesudah itu jika keadaan S akan berubah ubah, keluaran tetap 1. Yang artinya penahan NAND akan tetap menahan data pertama yang masuk, selama dalam keadaan ini penahan NAND berada dalam keadaan HOLD

3. Keadaan RESET.

Diagram Masukan

Pada keadaan ini, keluaran Q tetap 1 (tinggi) apapun yang terjadi pada S. Cara menurunkan pulsa dari 1 menjadi 0 adalah mengaktifkan R. Begitu R berubah keadaannya dari 1 menjadi 0 maka seketika itu juga keluaran Q akan menjadi 0. Dan R hanya sekali saja berperan dalam mengubah keadaan keluaran Q. Setelah itu apapun yang terjadi pada R tidak akan ditangga pi oleh keluaran Q.

REFERENSI :

Komentar

Posting Komentar